University of Iowa Iowa Research Online

Theses and Dissertations

Fall 2014

# Generation of compact test sets and a design for the generation of tests with low switching activity

Amit Kumar University of Iowa

Follow this and additional works at: https://ir.uiowa.edu/etd

Part of the Electrical and Computer Engineering Commons

Copyright 2014 Amit Kumar

This dissertation is available at Iowa Research Online: https://ir.uiowa.edu/etd/1476

# **Recommended Citation**

Kumar, Amit. "Generation of compact test sets and a design for the generation of tests with low switching activity." PhD (Doctor of Philosophy) thesis, University of Iowa, 2014. https://doi.org/10.17077/etd.93exb2ob

Follow this and additional works at: https://ir.uiowa.edu/etd

# GENERATION OF COMPACT TEST SETS AND A DESIGN FOR THE GENERATION OF TESTS WITH LOW SWITCHING ACTIVITY

by

Amit Kumar

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

December 2014

Thesis Supervisors: Professor Sudhakar M. Reddy Dr. Janusz Rajski

Graduate College The University of Iowa Iowa City, Iowa

# CERTIFICATE OF APPROVAL

# PH.D. THESIS

This is to certify that the Ph.D. thesis of

Amit Kumar

has been approved by the Examining Committee for the thesis requirement for the Doctor of Philosophy degree in Electrical and Computer Engineering at the December 2014 graduation.

Thesis Committee: \_\_\_\_\_

Sudhakar M. Reddy, Thesis Supervisor

Janusz Rajski, Thesis Supervisor

Jon G. Kuhl

David R. Andersen

Mona K. Garvin

Hantao Zhang

To My Parents

# ACKNOWLEDGEMENTS

I would like to thank my thesis supervisors Professor Sudhakar M. Reddy and Dr. Janusz Rajski for all their support and guidance throughout the years of my graduate work.

I am also thankful to my thesis committee members for their encouragement and support.

Finally, I would like to thank my friends and family for their love and support.

## ABSTRACT

Test generation procedures for large VLSI designs are required to achieve close to 100% fault coverage using a small number of tests. They also must accommodate on-chip test compression circuits which are widely used in modern designs. To obtain test sets with small sizes one could use extra hardware such as test points or use software techniques. An important aspects impacting test generation is the number of specified positions, which facilitate the encoding of test cubes when using test compression logic. Fortuitous detection or generation of tests such that they facilitate detection of yet not targeted faults, is also an important goal for test generation procedures.

At first, we consider the generation of compact test sets for designs using onchip test compression logic. We introduce two new measures to guide automatic test generation procedures (ATPGs) to balance between these two contradictory requirements of fortuitous detection and number of specifications. One of the new measures is meant to facilitate detection of yet undetected faults, and the value of the measures is periodically updated. The second measure reduces the number of specified positions, which is crucial when using high compression. Additionally, we introduce a way to randomly choose between the two measures.

We also propose an ATPG methodology tailored for BIST ready designs with X-bounding logic and test points. X-bounding and test points used to have a significant impact on test data compression by reducing the number of specified positions.

We propose a new ATPG guidance mechanism that balances between reduced specifications in BIST ready designs, and also facilitates detection of undetected faults. We also found that compact test generation for BIST ready designs is influenced by the order in which faults are targeted, and we proposed a new fault ordering technique based on fault location in a FFR. Transition faults are difficult to test and often result in longer test lengths, we propose a new fault ordering technique based on test enumeration, this ordering technique and a new guidance approach was also proposed for transition faults. Test set sizes were reduced significantly for both stuck-at and transition fault models.

In addition to reducing data volume, test time, and test pin counts, the test compression schemes have been used successfully to limit test power dissipation. Indisputably, toggling of scan cells in scan chains that are universally used to facilitate testing of industrial designs can consume much more power than a circuit is rated for. Balancing test set sizes against the power consumption in a given design is therefore a challenge. We propose a new Design for Test (DFT) scheme that deploys an on-chip power-aware test data decompressor, the corresponding test cube encoding method, and a compression-constrained ATPG that allows loading scan chains with patterns having low transition counts, while encoding a significant number of specified bits produced by ATPG in a compression-friendly manner. Moreover, the new scheme avoids periods of elevated toggling in scan chains and reduces scan unload switching activity due to unique test stimuli produced by the new technique, leading to a significantly reduced power envelope for the entire circuit under test.

## PUBLIC ABSTRACT

Test set size is known to increase at a faster rate than device size. Test cost for a given circuit is directly proportional to the number of independent test data inputs called test vectors, hence reducing the number of test vectors reduces test cost. Automatic Test Pattern Generation (ATPG), a tool, used to generate test patterns is used to generate tests. Decisions made while generating tests play an important role and should be made in a manner to facilitate detection of undetected faults. Since, modern design use compression logic a mechanism in which only a given number of deterministically specified positions can be encoded, reduction in the number of specified positions is a necessity.

We first propose new heuristics for making ATPG decisions based on undetected faults. The heuristics presented create appropriate balance between two contradictory requirements of allowing a test to facilitate detection of undetected faults and the number of specified positions in tests. Further, we propose an ATPG methodology to reduce test set sizes when additional hardware is used to improve test pattern counts. Next we propose a new fault ordering scheme based on ease of detection of a fault which also aids in reducing test pattern counts.

When a chip is tested, usually power dissipation is more than functional specifications leading to over-stressing of tested chips, potentially causing damage to chips during test. We also propose, what we call Isometric Compression Scheme to simultaneously reduce test power and test set size.

# TABLE OF CONTENTS

| LIST ( | OF TA                                           | ABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST ( | OF FI                                           | GURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CHAP   | TER                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1      | INT                                             | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5 \\ 1.6 \\ 1.7$ | Testing Basics21.1.1Scan Chains3Fault Models6Scan Types8Built-In Self-Test9Test Generation11Test Points and X-bounding Logic12Test Compression14                                                                                                                                                                                                                                                                                                                                                                        |

|        | 1.8                                             | Test Compaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | 1.9                                             | Overview of the Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2      | PRE                                             | EVIOUS WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 2.1                                             | ATPG Algorithms       21         2.1.1       D-Algorithm       23         2.1.2       PODEM       24         2.1.3       FAN       25         2.1.4       SOCRATES       26         2.1.5       Recursive Learning       27         2.1.6       SPOP       27                                                                                                                                                                                                                                                           |

|        | 2.2                                             | Test Set Compaction       27         2.2.1       Compaction Approach by Goel and Rosales       28         2.2.2       COMPACTEST       29         2.2.3       ROTCO       30         2.2.4       COMPACT       31         2.2.5       CODEM       31         2.2.6       Double Detection and Two-by One       32         2.2.6.1       Double Detection       32         2.2.6.2       Two-by-One Approach       34         2.2.8       Mintest       34         2.2.9       Forward Looking Fault Simulation       35 |

|   |     |         |                                                            | 35 |

|---|-----|---------|------------------------------------------------------------|----|

|   |     |         | 0 1                                                        | 36 |

|   |     |         | J.                                                         | 37 |

|   |     |         | 1 1                                                        | 37 |

|   |     |         |                                                            | 38 |

|   | 2.3 | Comp    | 00 0                                                       | 38 |

|   |     | 2.3.1   | 0 1                                                        | 39 |

|   |     | 2.3.2   | 0                                                          | 40 |

|   |     | 2.3.3   | 9 I                                                        | 40 |

|   |     | 2.3.4   | Previous Work In Low Power Compression                     | 40 |

| 3 | GEN | NERAT   | ION OF COMPACT TEST SETS                                   | 45 |

|   | 3.1 | Fault 1 | Based ATPG Decisions                                       | 47 |

|   | -   | 3.1.1   | Overview of the proposed method for line justification and |    |

|   |     | 0       | •                                                          | 47 |

|   |     | 3.1.2   |                                                            | 47 |

|   |     | 3.1.3   | 8                                                          | 49 |

|   |     | 3.1.4   |                                                            | 51 |

|   |     | 0       | 3.1.4.1 Dynamic Measure for Guiding Line Justification     | -  |

|   |     |         | · ·                                                        | 51 |

|   |     |         |                                                            | 53 |

|   |     | 3.1.5   | · · ·                                                      | 56 |

|   |     |         | 3.1.5.1 Line Justification Decisions Using Dynamic Mea-    |    |

|   |     |         | 0 0                                                        | 57 |

|   |     | 3.1.6   |                                                            | 57 |

|   | 3.2 |         | 1 0                                                        | 58 |

|   |     | 3.2.1   |                                                            | 60 |

|   |     | 3.2.2   | 0 0 ·                                                      | 62 |

|   |     | 3.2.3   |                                                            | 63 |

|   |     |         |                                                            | 65 |

|   |     | 3.2.4   |                                                            | 68 |

|   |     |         | 3.2.4.1 S Guidance Measures                                | 68 |

|   |     |         |                                                            | 69 |

|   |     | 3.2.5   |                                                            | 70 |

|   |     | 3.2.6   |                                                            | 71 |

|   | 3.3 | Transi  |                                                            | 72 |

|   |     | 3.3.1   |                                                            | 74 |

|   |     |         | 0                                                          | 75 |

|   |     |         |                                                            | 77 |

|   |     |         |                                                            | 78 |

|   |     | 3.3.2   |                                                            | 78 |

|   |     |         |                                                            | 79 |

|   |     |         | 1 0                                                        | 81 |

|   |     |         |                                                            |    |

|    | 3.4  | Exper  | imental Results                                | 82  |

|----|------|--------|------------------------------------------------|-----|

|    |      | 3.4.1  | Fault-Based ATPG                               | 82  |

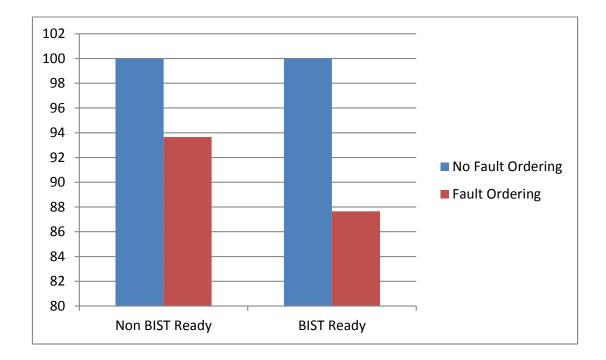

|    |      | 3.4.2  | Experimental Results for BIST Ready ATPG       | 85  |

|    |      | 3.4.3  | Results for Transition Faults                  | 87  |

|    |      |        |                                                |     |

| 4  | ISO  | METRI  | IC TEST COMPRESSION                            | 91  |

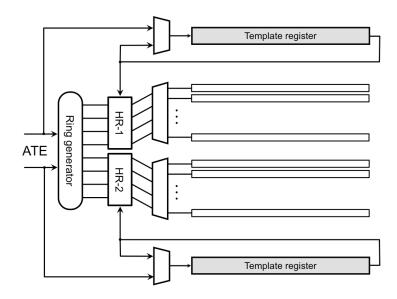

|    | 4.1  | Isome  | tric Architecture                              | 92  |

|    |      | 4.1.1  | Overview of Isometric Compression Scheme       | 93  |

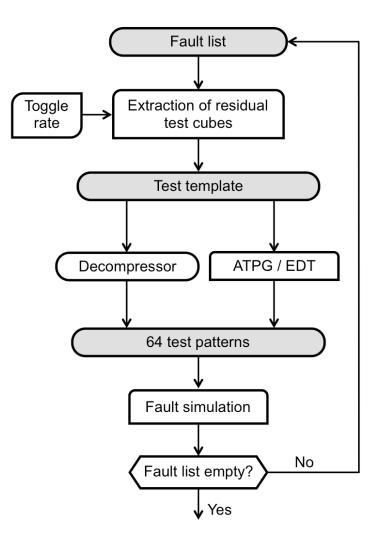

|    | 4.2  |        | tric Compression Flow                          | 97  |

|    | 4.3  |        | ual Test Cubes Generation                      | 100 |

|    |      | 4.3.1  | Extraction of Residual Test Cube               | 101 |

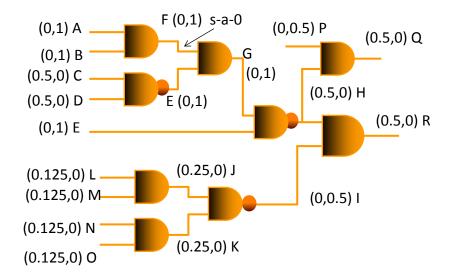

|    |      | 1.0.1  | 4.3.1.1 Procedure to Calculate Probability     | 102 |

|    |      | 4.3.2  | Typical Residual Cube Profile                  | 104 |

|    | 4.4  |        | Template Generation                            | 106 |

|    |      | 4.4.1  | Covering Algorithm                             | 107 |

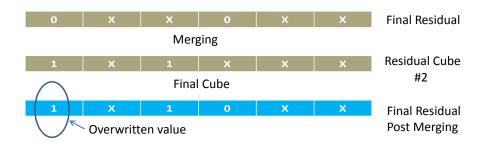

|    |      | 4.4.2  | Rules for Conflict Based Merging               | 109 |

|    |      | 4.4.3  | Assigning ATPG Constraints and Equivalences    | 110 |

|    |      | 4.4.4  | EDT Solver and Test Template                   | 112 |

|    |      | 4.4.5  | Algorithmic Overview                           | 113 |

|    | 4.5  | -      | ple Template                                   | 115 |

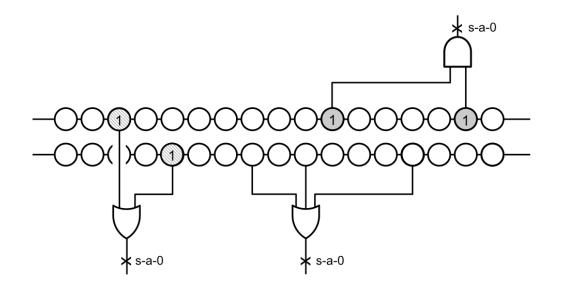

|    |      | 4.5.1  | Hardware Architecture                          | 115 |

|    |      | 4.5.2  | Overall Flow                                   | 115 |

|    |      | 4.5.3  | Procedure to Generate Scan Groups:             | 117 |

|    | 4.6  |        | tric Patterns and Compression                  | 118 |

|    | 4.7  |        | imental Results                                | 121 |

|    |      | 4.7.1  | Results for Stuck-at Faults                    | 121 |

|    |      | 4.7.2  | Comparison With a Low-Power Compression Scheme | 127 |

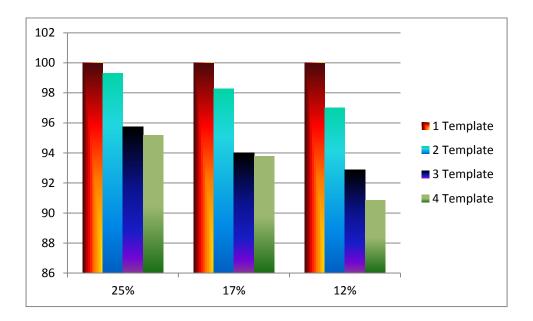

|    |      | 4.7.3  | Impact of Using Multiple Templates             | 127 |

|    |      | 4.7.4  | Comparison With Other ATPG Techniques          | 128 |

|    |      | -      |                                                | -   |

| 5  | COI  | NCLUS  | IONS                                           | 129 |

|    | 5.1  | Future | e Work                                         | 130 |

| RI | EFER | ENCE   | S                                              | 132 |

|    |      |        |                                                |     |

# LIST OF TABLES

| Tabl | e                                                                                                                                                    |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

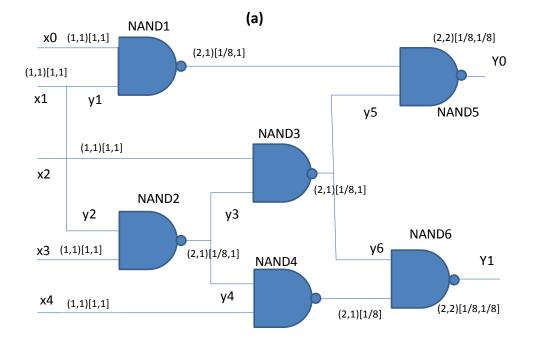

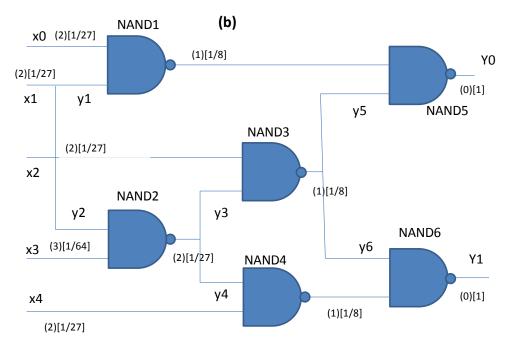

| 3.1  | Calculation $SCOAP$ controllability and observability values                                                                                         | 45  |

| 3.2  | Circuit Properties                                                                                                                                   | 46  |

| 3.3  | Test length Random and SCOAP                                                                                                                         | 46  |

| 3.4  | Probability $p$ calculation $\ldots \ldots \ldots$ | 48  |

| 3.5  | Comparison of the Proposed and Random Decision                                                                                                       | 81  |

| 3.6  | Effect of Compression Ratio                                                                                                                          | 81  |

| 3.7  | Results when $p$ is $1/2$ for all gates $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                               | 83  |

| 3.8  | Results using only static guidance measures                                                                                                          | 83  |

| 3.9  | Results using only dynamic measures                                                                                                                  | 84  |

| 3.10 | Comparison of fault ordering methods                                                                                                                 | 85  |

| 3.11 | Results for non-BIST ready designs                                                                                                                   | 86  |

| 3.12 | Results for transition fault ATPG                                                                                                                    | 88  |

| 3.13 | Results using only dynamic measures                                                                                                                  | 88  |

| 3.14 | Results with only static measures                                                                                                                    | 89  |

| 3.15 | Results with only fault ordering                                                                                                                     | 89  |

| 4.1  | Circuit Properties                                                                                                                                   | 121 |

| 4.2  | Test Length for Various Switching Rates and Multiple Templates                                                                                       | 125 |

| 4.3  | Volume for Various Switching Rates and Multiple Templates                                                                                            | 125 |

| 4.4  | Toggling Rates (WTM) Scan Shift-in                                                                                                                   | 126 |

| 4.5 | Toggling Rates (WTM) Scan Shift-out | 126 |

|-----|-------------------------------------|-----|

| 4.6 | Results for non-BIST ready designs  | 127 |

# LIST OF FIGURES

| Figu | Ire                                                     |    |

|------|---------------------------------------------------------|----|

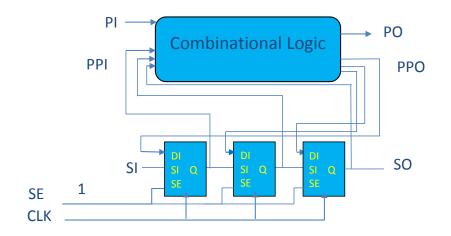

| 1.1  | Scan Chains                                             | 4  |

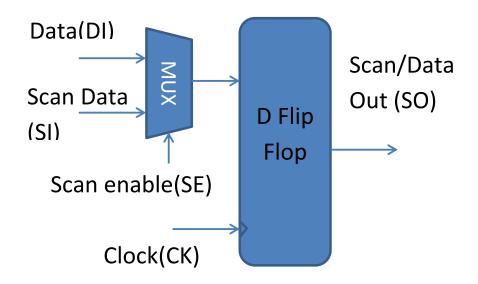

| 1.2  | Muxed – Scan Flip-flop                                  | 5  |

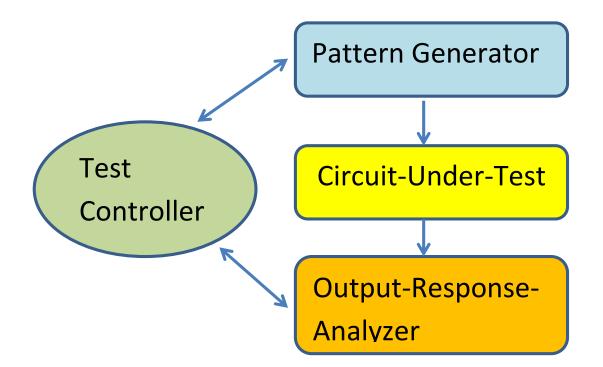

| 1.3  | BIST scheme                                             | 10 |

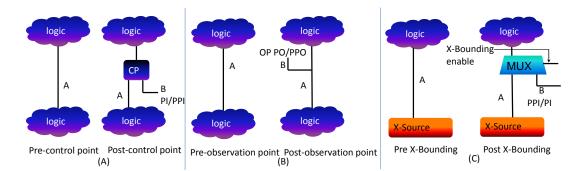

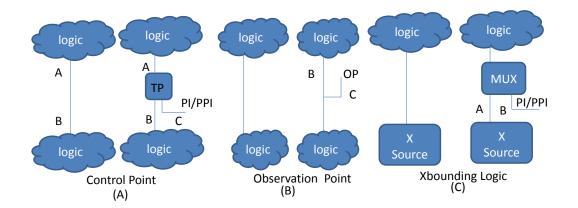

| 1.4  | Control/Observation point and x-bounding logic          | 12 |

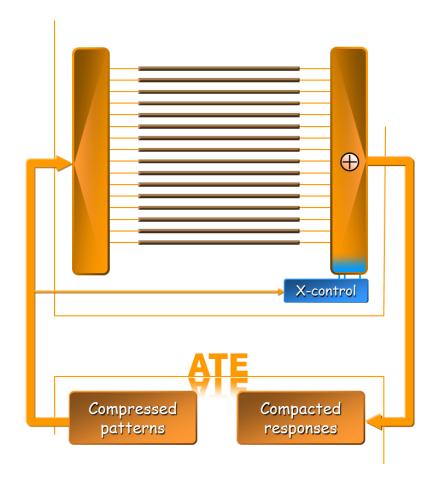

| 1.5  | EDT Architecture                                        | 15 |

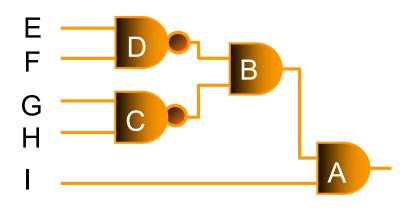

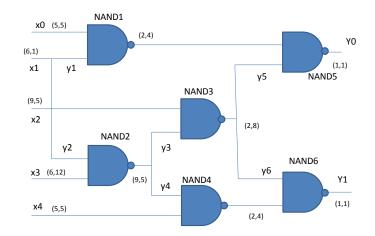

| 2.1  | Example Circuit                                         | 22 |

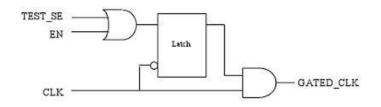

| 2.2  | A typical clock gating circuit                          | 41 |

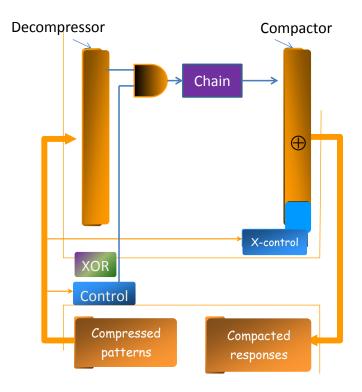

| 2.3  | Low Power EDT                                           | 42 |

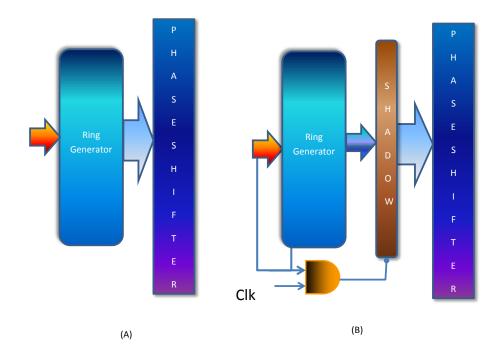

| 2.4  | Decompressor (A) Original (B) With shadow register      | 43 |

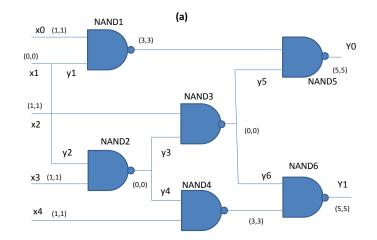

| 3.1  | SJ0 and $SJ1$ measures                                  | 50 |

| 3.2  | SP measures                                             | 50 |

| 3.3  | Calculation of $DMJ^1$ and $DMJ^0$                      | 52 |

| 3.4  | Calculation of DMJ values                               | 53 |

| 3.5  | Calculation of $DMP^1$ and $DMP^0$                      | 54 |

| 3.6  | Calculation of DMP values                               | 55 |

| 3.7  | (A) Control Points (B) Observation Points(C) X-bounding | 60 |

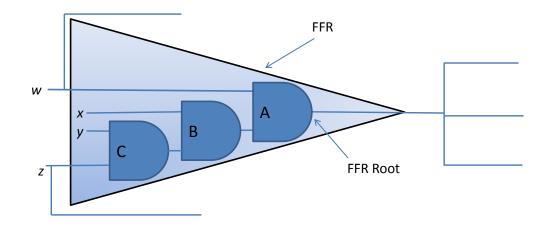

| 3.8  | Fan-out free region.                                    | 63 |

| 3.9  | FFR height-based fault ordering procedure.              | 66 |

| 3.10 | Number of specifications and fault ordering.            | 67 |

| ļ | 3.11 | Calculation of $TEJ^1$ and $TEJ^0$            | 76  |

|---|------|-----------------------------------------------|-----|

| ļ | 3.12 | Calculation of $TEP^1$ and $TEP^0$            | 77  |

| ę | 3.13 | Generation of Final Fault Order               | 79  |

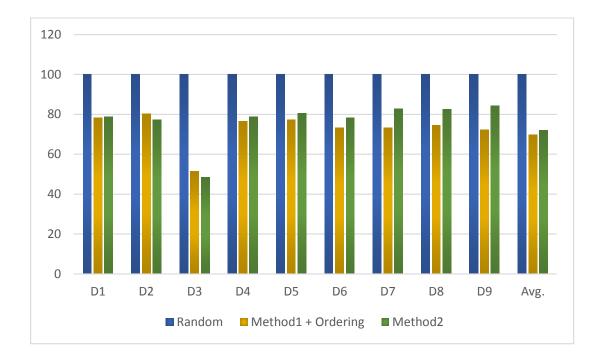

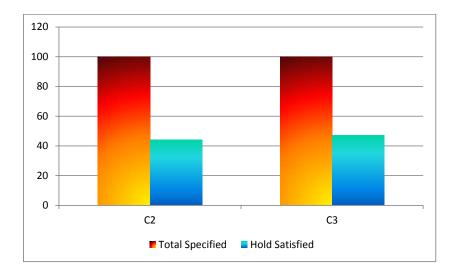

| • | 3.14 | Test length comparison for BIST ready designs | 87  |

| ļ | 3.15 | Runtime comparison for non BIST ready designs | 88  |

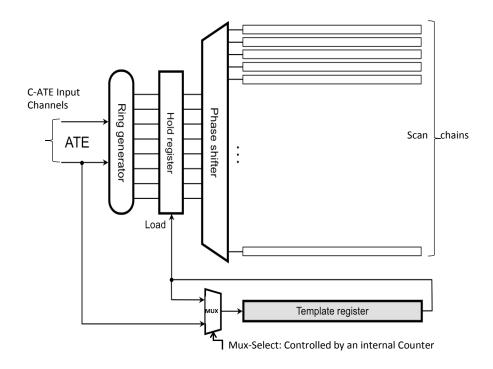

| 2 | 4.1  | Isometric Decompressor                        | 92  |

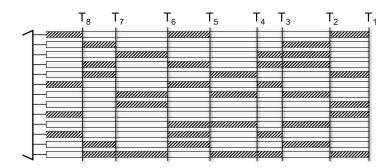

| 2 | 4.2  | Low power template                            | 93  |

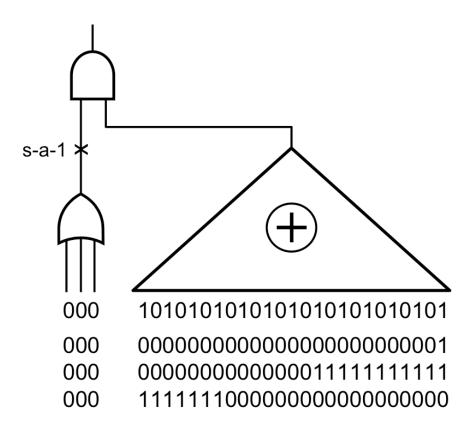

| 2 | 4.3  | Circuit test cubes                            | 95  |

| 2 | 4.4  | Isometric compression flow                    | 97  |

| 2 | 4.5  | Extraction of residual test cube              | 101 |

| 2 | 4.6  | Calculation of probabilities for a fault      | 102 |

| 2 | 4.7  | Computing probabilities                       | 103 |

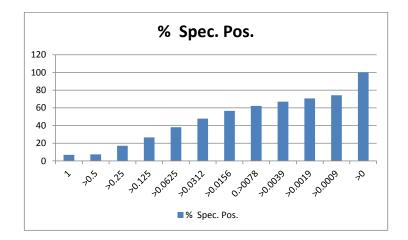

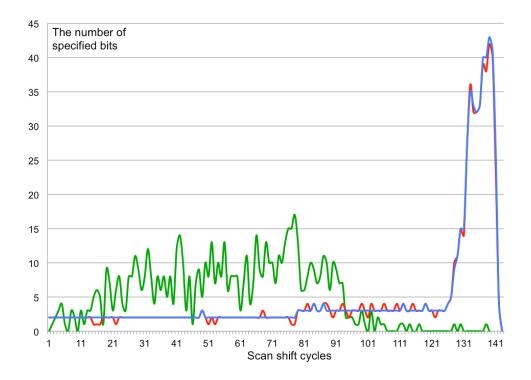

| 2 | 4.8  | Specified bits profile                        | 105 |

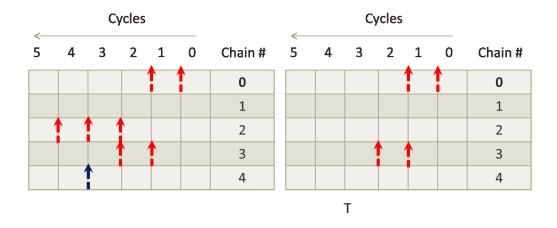

| 2 | 4.9  | Toggle points and spans                       | 106 |

| 2 | 4.10 | Procedure to generate test templates          | 108 |

| 2 | 4.11 | Covering Algorithm                            | 109 |

| 2 | 4.12 | Conflict Based Merging                        | 109 |

| 2 | 4.13 | EDT solver and the test template              | 112 |

| 2 | 4.14 | Multiple test template usage                  | 116 |

| 2 | 4.15 | Specified position histogram                  | 119 |

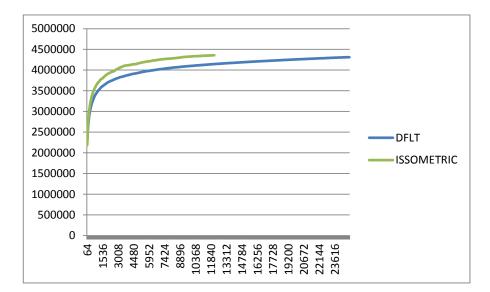

| 2 | 4.16 | Number of faults detected                     | 120 |

| 2 | 4.17 | Distribution of specified bits                | 122 |

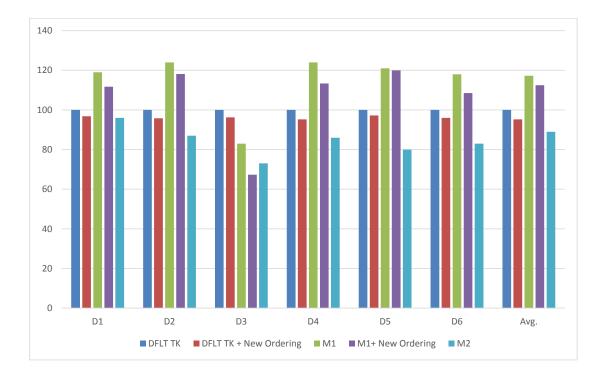

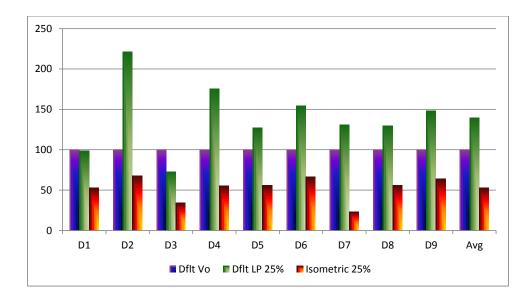

| 4.18 | Comparison with default low power scheme               | 124 |

|------|--------------------------------------------------------|-----|

| 4.19 | Single and multiple templates for various toggle rates | 124 |

# CHAPTER 1 INTRODUCTION

In deep submicron era device complexity is increasing at a phenomenal rate. On the same sized die, roughly double the number of transistors are printed every eighteen months. This increasing density of fabrication also leads to new problems. It is becoming increasingly difficult to verify that chips which are manufactured match their functional and operating specifications. Since a percentage of devices manufactured usually do not comply with operating requirements, it is important to screen them out by testing the manufactured devices in an efficient and cost-effective manner. Unfortunately test cost is known to increase at a faster rate than device size. Additionally, due to non-functionality of tests, applied over-testing can affect yield and impact future operations of device functionality [1, 2, 3]. When a chip is tested, usually power dissipation is more than functional specifications leading to over-stressing of tested chips, causing reliability failures and defects that may usually not show up in normal functional operations. It is therefore important to test chips without compromising chip quality and reliability.

In this thesis, we report methods that address some of these concerns. We address two problems with tests in this work: test data volume (amount of data that needs to be loaded into a tester) and test application time. Test data volume for a given circuit is directly proportional to the number of independent test data input sequences known as test vectors, hence reducing the number of test vectors reduces test data volume. Usually test data volume is proportional to test application time:

time (cycles) required to apply a test to a circuit under test in the context of present work; however, exceptions are known [4]. We present two novel techniques that we introduced [5, 6] to reduce test set sizes in this report. Next, we will also propose work on test power reduction in the latter part of this thesis [7].

#### 1.1 Testing Basics

A manufacturing test is typically performed once the chip has been manufactured to screen for defective circuits [1, 2, 8]. A typical industrial test environment consists of a circuit under test (CUT) and equipment called Automatic Test Equipment (ATE). Usually for economic reasons, test time on an ATE is costly. An ATE has finite memory and stores some vectors to apply them to the chip. ATE subsequently observes the generated response of these vectors and compares them to expected "golden" responses. If the chip response deviates from golden response, in most cases the chip is marked as faulty and is discarded. In some cases, if the chip complies with most of the existing parameters but does not meet stringent operating criteria like speed or temperature, the chip can still be used after marking (binning) as a lower—quality chip that may be used by low end customers. In case of memories, some connections may be reconfigured to render the chip re-usable; however, it requires having some additional redundancy on the chip itself [2].

The test vectors stored on an ATE and golden responses are generated using a software program named ATPG (Automatic Test Pattern Generator) [9, 10]. As the name suggests, an ATPG automatically generates a test set that can possibly

separate faulty and non-faulty chips. ATPG usually can operate on two circuit types combinational and sequential circuits.

A combinational circuit has no memory element in it. It is comparatively easier for an ATPG to generate test patterns for combinational circuits, since current input values exclusively determine output values. Test generation for sequential circuits requires, sequential elements in the circuit to be set to desired values. In this case, the ATPG needs to create test sequences over many clock cycles to set desired sequential elements to a desired value. Sequential circuit test generation is typically more complex in comparison to combinational circuit test generation.

ATPG commonly uses scan—inserted designs for test generation. Scan insertion converts a sequential design into a combinational one in test mode [11]. Flip-flops in any design are usually not controllable or observable from the output. A proper initialization sequence may be required to initialize a flip-flop. We connect flip-flops in design in the form of shift registers named scan-chains to provide full controllability — a way to initialize flip-flops with a given value and observability — to observe what value was present in a given flip-flop. Next, we discuss more details about scan chains.

## 1.1.1 Scan Chains

Scan design provides the necessary controllability of a flip-flop by connecting all flip-flops in a design in the form of one or more shift registers during testing (in test mode) called scan-chains, as shown in Figure 1.1. When the test mode signal

Figure 1.1: Scan Chains

is disabled, the circuit is logically equivalent to its functional mode. The inputs and outputs of the shift registers obtained are made into primary output and input, respectively. Because there are two input sources for a scan cell (flip-flops in a scan chain), a selection mechanism must be provided to allow a scan cell to operate in two different modes: normal/capture mode, and shift mode. In normal/capture mode, data input is selected to update the output. In shift mode, scan input is selected to update the output. If n is the number of flip-flops in a scan-chain we can control or observe any flip-flop in maximum n shifts. Various scan chain methods are used. The commonly used methodology is replacing design flip-flops with Muxed scan flops. Since scan-chains provide full controllability and observability, the output of a scancell is similar to a primary input and is called Pseudo-Primary Input (PPI) and,

4

Figure 1.2: Muxed – Scan Flip-flop

similarly, input of a scan-cell is essentially a primary output called Pseudo-Primary Output (PPO), as shown in Figure 1.1.

Muxed Scan Cell: This is the most widely used scan-cell design [1, 2]. Muxed scan cell shown in Figure 1.2 consists of a D flip-flop and a multiplexer. The multiplexer select input is controlled by scan enable (SE) input to select between the data input (DI) and the scan input (SI). Muxed scan cell is the most common form of scan cell used in practice.

ATPG operates on a logical abstraction of real defects called faults. Test generation complexity is heavily dependent on the target fault type. In the next section, we discuss some common fault models.

#### 1.2 Fault Models

Fault models are logical abstractions of real defects. Using a logical fault model makes it easier to simulate the impact of a real defect, to a large extent. However, in practice, fault models have their handicaps and not all defects can be modeled accurately with the same fault model. Using logic—level fault models can simplify simulating the fault effect caused by the real defect. Fault models, such as stuck-at fault model, bridge fault mode, open fault mode, transition fault model, path delay fault model, and cell internal fault mode are most commonly used.

Stuck-at fault model: A stuck-at-v [1] fault on a line l forces a logic value v on the line l. Line l can be primary inputs, primary outputs, gate inputs and outputs, fanout stems, and fanout branches. A stuck-at fault can be of two types: stuck at a constant value v, where v is 0 or 1, referred to as stuck-at-0 (SA0), or stuck-at-1 (SA1), respectively.

Transition fault model: In some cases, gate delay causes the gate to switch at a lower than normal speed when its inputs change. When this delay is large enough, the defect is modeled as a transition delay fault [12]. A transition delay fault occurs when the time required for switching outputs from 0 (1) to 1 (0) in the gate, due to a change in the gates inputs, takes substantially (infinitely) longer than its normal time. Slow change from 0(1)-to-1(0) is called slow-to-rise (fall) fault.

Path Delay Fault Model: The path delay fault model focuses on the testing of a set of predefined paths in order to detect the cumulative delays along these paths [13]. A path is a set of gates which starts at a PI/PPI and ends at PO/PPO. The

path delay fault model takes the cumulative delays along a path into account, while the transition fault model accounts for gross gate delay on a gate input or output. Path delay fault is more comprehensive but not used extensively, due to complex ATPG process and unmanageable test set sizes.

Cell Aware Fault Model: Some fault models were proposed to describe the defects inside a (complex) gate. Instead of modeling the defects at inputs and outputs of gates, the internal defect models -- such as stuck-at fault, stuck-open fault, resistive-open fault and short/bridge -- represent the internal defects existing in and between transistors and interconnects inside gates [14].

Bridge fault model: An unintended short between two circuit elements is commonly referred to as a bridging fault [15, 16]. These elements can be transistor terminals or connections between transistors and gates. The case of an element being shorted to power (VDD) or ground (VSS) is equivalent to the stuck-at fault model; however, when two signal wires are shorted together, bridging fault models are required.

The number of faults detected by a test set (group of tests) can be reported in two formats:

• Fault Coverage: Percentage of faults detected out of the total number of faults present in the modeled fault set.

• Test Coverage: Percentage of faults detected from the list of detectable faults. The above fault models are most commonly used during test generation with ATPG. In most cases, stuck-at fault ATPG is modified to generate test sets for other fault

models. Typically ATPG uses combinational or scan–inserted circuits to generate necessary test sets.

#### 1.3 Scan Types

Some other common scan variations that are used are:

*Clock Scan Cell:* Input selection in clocked scan is conducted using two independent clocks; data clock DCK and shift clock SCK [1, 2]. In shift mode, SCK is high and is used to shift data into scan-cell. If data needs to be shifted, then DCK is used to shift data into the scan cell.

Level Sensitive Scan Cell: In order to guarantee race-free operation, three clocks -- A, B, and C -- are applied in a non overlapping manner. Advantage: The scan can be applied to latch based design [1, 11].

Replacing all flip-flops in a design with scan cells and stitching them in scan chain is called full scan architecture. Various types of other scan architecture were proposed in literature:

*Partial Scan:* Unlike full-scan design, where all storage elements in a circuit are replaced with scan cells, partial-scan [17] design only requires that a subset of storage elements be replaced with scan cells and connected into scan chains.

Random Access Scan: Makes each scan cell randomly and uniquely addressable, similar to storage cells in a random-access memory (RAM) [18]. Its advantages lie in reducing test power and test data required for testing. However, routing (interconnections wire length) and additional hardware required are high.

*Enhanced Scan:* Enhanced scan [19] increases the capacity of a typical scan cell by allowing it to store two bits of data that can be applied consecutively to the combinational (functional) logic driven by the scan cells.

#### 1.4 Built-In Self-Test

Traditional test techniques that use ATPG to target single faults for digital circuit testing have become quite expensive. One approach to alleviate these testing problems is to incorporate Built-in Self-Test (BIST) [1, 20, 2] features into a digital circuit at the design stage. With logic BIST, circuits that generate test patterns and analyze the output responses of the functional circuitry are embedded in the chip.

BIST has several advantages. BIST eliminates the huge test data volume necessary to store the output responses for comparison. Moreover, a circuit embedded with BIST circuitry can be easily tested after being integrated into a system or infield. Another advantage of BIST is that it aids multiple detection of a fault, which is known to detect more non-modeled faults.

A typical Built-in-Self Test (BIST) [1, 20] scheme shown in Figure 1.3 consists of a test pattern generator (TPG) (usually a linear feedback shift register) which automatically generates test patterns. Usually random patterns are used, however variations such as weighted random patterns or patterns with low-switching activity may also be used. The test patterns generated by a TPG are applied to the inputs of the circuit under test (CUT). The output obtained is observed in a compressed form called signature by an output response analyzer (ORA). The output signature

Figure 1.3: BIST scheme

observed by ORA is rendered useless even if a single unknown value referred to as X reaches the ORA. An application—specific BIST controller applies scan-enable, clocks, and other control signals in a required sequence. The logic BIST controller compares the obtained response with the expected response captured by ORA, and decides on pass/fail.

However, logic BIST patterns are usually aided by other patterns like stored patterns or externally applied patterns to achieve complete coverage. Problems faced by logic BIST are:

• Typically fault coverage is very low.

- Extra hardware in the form of test points (hardware to make faults in the CUT testable by pseudo-random patterns) is required to increase coverage [21, 22].

- X-bounding [23] (masking all x-sources by known value during testing) needs to be performed to suppress all Xs in the design from reaching the ORA.

- Usually large numbers of patterns are required.

A design has to be rendered BIST-ready (with test points and x-source blocking) to apply BIST for testing. Next, we discuss directly generating patterns using an ATPG.

# 1.5 Test Generation

Test generation process strives to generate a test set which can detect all the targeted faults. Faults are usually of the same fault model, but a mix of faults from various fault models can also be used.

The patterns in the test set are ultimately intended to detect defects occurring in the circuit due to flaws in the manufacturing process. Test generation consists of two main steps: fault activation and (fault effect) propagation [1, 9], described below.

- Fault activation: Fault activation sets the signal on a given line to a given value, depending on the fault model. For stuck-at faults, a value opposite to that produced by a fault is used in order to excite the fault. In case of transition fault model activating, a fault needs to be assigned two different values to fault site in consecutive clock cycles.

- Fault propagation: Fault effect propagation means to set proper values to the

Figure 1.4: Control/Observation point and x-bounding logic

off-path inputs along a selected path so that the path is sensitized and the fault effect can be observed at an observation point.

*Example:* Given an AND gate with inputs A, B and output C. To detect a stuck at 1 fault at the input A, the fault needs to be activated by placing an opposite value of the fault type on A, i.e. a 0. To propagate the fault effect to output C, B should be 1 (if B is assigned a value of 1 the output value is uniquely determined by the value at line A). In case of a fault-free circuit, C is assigned a 0; if a stuck-at 1 fault exists on A, C takes the value 1.

## 1.6 Test Points and X-bounding Logic

In BIST, the fault coverage is limited by the presence of random pattern—resistant faults. Test point [21, 22, 24, 25, 26] adds control points and observation points for providing additional controllability and observability to improve the detection probability of random pattern resistant faults so they can be detected during BIST. However, test points can also be used to reduce test set sizes for an ATPG [24]. Test

points are of two types: control points and observation points. Figure 1.4 (A) and Figure 1.4(B) show a basic implementation of control points and observation points, respectively. In Figure 1.4(A), a control point is inserted to increase the controllability of line A. A two input AND (OR) gate is used in place of CP for zero(one) control point. A zero control point needs only one input B as 0 to place a 0 on line A.

Similarly, an observation point in its simplest form is a simple connection from line A to PO/PPO, as shown in Figure 1.4(B). Any values on line A can be directly observed on PO/PPO.

A control point  $v \in (0, 1)$  is typically inserted at a line l to set its value to a value which is difficult to obtain through circuit input values; the difficulty is measured by what are called testability measures, of which SCOAP [1] is the most commonly used. When SCOAP [1] controllability of v is high indicating that setting l to v is difficult, a typically large number of inputs are needed to be set to desired values to justify the value v on l. The addition of a control point reduces SCOAP controllability of v to the least value, and ATPG decisions for a value v on line l are typically guided toward control points if ATPG makes decisions based on SCOAP values. Similarly the addition of an observation point reduces SCOAP observability of a line, and an observation point is used for facilitating observation of fault effect values referred to as D or  $\overline{D}$ . The insertion of test points impacts ATPG decisions using controllability and observability. This may have an adverse effect on the detection of yet – undetected faults during the generation of small test sets unless ATPG decisions are properly guided.

An X-source is any circuit element whose output can exhibit unknown (X) behavior during a test. Because any unknown (X) value that propagates directly or indirectly to the output response analyzer will corrupt the signature and cause the BIST design to malfunction, no unknown (X) values can be tolerated. Any unknown (X) source in the BIST-ready core, which is capable of propagating its unknown (X) value to the ORA directly or indirectly, must be blocked and fixed using a DFT repair approach often called X-bounding. Figure 1.4(C) shows a typical X-bounding mechanism using a MUX. A MUX control point is placed on the line feed by X-source to place a constant 1 or 0 on it.

An X-source in a circuit is typically assigned very high controllability; bounding X-source reduces SCOAP controllability for both 0 and 1 for the X-source. Making justification decisions to be guided toward X-bounding [22] logic reduces the number of specifications required for line justification. Hence, X-bounding has the similar impact as a 1 or 0 control point on a line l.

#### 1.7 Test Compression

With ever increasing device complexity and size, new kinds of defects are becoming dominant and test sets for existing fault sets are growing. Tests for additional fault models like transition and bridging fault models are becoming necessary. All the above result in the increase of data that is needed to be stored on a tester. However, tester memory is costly and it may be impractical to increase tester memory.

To deal with this issue, test compression schemes were proposed. Various

Figure 1.5: EDT Architecture

compression schemes reduce the amount of data needed to be stored on the tester. Koneman [27] was the first to propose the idea of LFSR reseeding, which forms the backbone for some of the commonly—used compression schemes.

Another advantage of test compression schemes is that a low-cost tester may be used for testing instead of upgrading the tester. Test compression schemes usually

consist of an on-chip decompressor that decompresses the encoded test stimuli values, and a compactor that compacts the output response obtained.

Test data is highly compressible as typically only 1 to 5% of the bits in a test have specified values. Specified values of test cubes are known to be highly correlated due to structural relations in the circuit.

In this work, we use designs with Embedded Deterministic Test (EDT) schemes [28] shown in Figure 1.5. EDT architecture consists of an on-chip decompressor located between the external scan input ports and the internal scan chains, as well as an onchip selective compactor inserted between the internal scan chains and the external scan output ports. The test data decompressor is implemented by a ring generator (optimized LFSR) and a phase shifter. The phase shifter is necessary to drive a large number of scan chains and to reduce linear dependencies between sequences entering the scan chains. In addition, the phase shifter design guarantees balanced use of all memory elements in the ring generator. Scan cells are divided evenly, if possible, into several shorter scan chains. For the purpose of producing the desired output, the ring generator is continuously seeded with data. The ratio between the inputs of the ring generator and the outputs of the phase shifter determines the maximum compression possible.

#### **1.8** Test Compaction

By test compaction or generation of compact tests, we mean the generation of small or minimal—sized test sets to achieve the desired fault coverage. Two methods

exist to generate minimal test sizes. The first approach is to use extra hardware such as test points. Another method uses software techniques to produce minimal test set sizes. In this work, we use software techniques. Several works have considered methods to generate compact (small) test sets. Generally, test-compaction procedures use static compaction or dynamic compaction or a combination of both [29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39]. Static compaction procedures merge compatible test cubes generated to detect individual faults [32, 33, 34]. They also use fault simulation of tests in test sets in different order(s) than the order in which the tests were generated to drop some tests in the test set. Tests are dropped without losing fault coverage. Dynamic compaction procedures use the unspecified values in a test cube to detect additional faults [29, 30, 31, 32, 35]. Generating tests with a minimal number of specified values help reduce the number of tests generated using static and dynamic compaction procedures. Tests with a minimum number of specified values also facilitate encoding of test cubes for designs with test compression logic, and hence aid generation of compact test sets for such designs.

A simple example of static compaction can be the case in which compatible vectors are identified in a test set made up of incompletely specified vectors. For example, vectors 11X1 and X101 are compatible. These two vectors can be combined and replaced by a vector 1101.

Dynamic compaction, on the other hand, tries to intelligently fill in the unspecified positions (Xs) in the test vectors such that more undetected faults can be detected. For example, consider an AND gate with inputs A, B and output C. Stuck-

at 1 fault at C can be detected by vector (A=0, B=X); however if we specify B=1, a test for stuck-at 1 at C is also a test for stuck-at 1 at A.

### 1.9 Overview of the Thesis

In Chapter 3, we give details about test set compaction making judicious ATPG decisions. We consider the generation of compact test sets for designs using on-chip test compression logic. Even though the proposed procedure can be used for designs without compression logic, the experiments we performed are all on designs with test compression logic. We introduce two new controllability and observability measures. Additionally, we introduce a way to randomly choose between the two proposed measures. One of the new controllability/ observability measures is meant to facilitate the detection of yet undetected faults similar to the Controllability/ C-observability measures in SCOAP and these values are periodically updated. However, the proposed measures for a line l differ from those of SCOAP as they take into consideration the yet undetected faults in the fan-in cone and fan-out cones of l. The main contributions of the completed work are:

- The new method to generate compact test sets is software—based and applicable to designs with and without on-chip test compression logic.

- Two new controllability and observability measures are given to guide line justification and fault propagation steps of ATPGs.

- A method to randomly select between the above two measures, depending on the logic level of the gates, is proposed.

- The techniques presented can be used together with some of the earlier methods such as delayed justification [39], and fault clustering [38].

- Experiments on several industrial designs show that the proposed techniques, on average, reduce the number of test patterns by about 24%, relative to that generated by a state-of-the-art commercial ATPG tool.

Later, we present a method to generate compact test sets for BIST ready designs: we observed that to take full advantage of the X-bounding and test points present in BIST ready designs generating compact (small) test sets, existing ATPGs may have to be modified. ATPGs should not only generate tests that detect targeted faults; while generating tests, one should also facilitate detection of yet undetected faults to generate close to minimal test sets . Specifically, always utilizing test points to derive tests may minimize specifications in tests, but usually will not facilitate detection of yet undetected faults.

We propose a new ATPG guidance mechanism that balances between reduced specifications in tests by using test points and bounded X-sources, and facilitating detection of yet undetected faults by exploring higher specification options with comparatively lower probability. We also found that compact test generation for BIST ready designs is influenced by the order in which faults are targeted, and we utilize this observation. A new fault ordering and guidance approach is proposed for transition faults. Ordering scheme balances between fortuitous detection capability and difficulty in detection, two reasons impacting test length to generate a fault order which produces compact test sets. A new guidance approach is also proposed for

transition faults.

In Chapter 4, we present a novel test data compression scheme to achieve higher compression with low toggling activity named *Isometric Compression Scheme* [7]. The new scheme deploys an on-chip power-aware test data decompressor, the corresponding test cube encoding method, and a compression-constrained ATPG that allows loading scan chains with patterns having low—transition counts while encoding a significant number of specified bits produced by ATPG in a compression-friendly manner. As a result, the new solution offers very high compression ratios and preserves all benefits of continuous flow compression. Moreover, the new scheme avoids periods of elevated toggling in scan chains and reduces scan unload switching activity due to unique test stimuli produced by the new technique, leading to a significantly reduced power envelope for the entire circuit under test.

The rest of this thesis is divided as follows: In Chapter 2, we discuss the previous work related to this thesis. In Chapter 3, we discuss the previous work in the field of ATPG for high compression. Details on the fault-based compaction mechanism we have proposed is discussed first. Later in Chapter 3, we present a new compact test generation methodology for BIST ready designs developed by us in Chapter 3. Isometric compression scheme is discussed in Chapter 4. We conclude the thesis in Chapter 5.

# CHAPTER 2 PREVIOUS WORK

In this chapter, we the discuss previous work relevant to our work. First, we will discuss ATPG for test generation.

## 2.1 ATPG Algorithms

In this section, we describe some of the basic terminologies that will be used in this work.

Sensitized Path: A path starting at line l is said to be a sensitized path if any value change on line l changes value of one or more PO/PPO.

Fault Detection: In a full scan circuit, a fault stuck-at-v is said to be detected if line l can be activated to  $\bar{v}$  and a path exists between line l and PO/PPO such that any change on line l also changes one of the specified PO/PPO.

Now we will define some more definitions commonly used by ATPG test generation programs. These are implication, justification, and fault effect propagation procedures.

*Implication:* It is the procedure to find all the uniquely determined signals under the current circuit state. Justification is responsible for selecting a way among several possible ways to achieve desired values on signal lines. Fault effect propagation takes care of selecting a path to propagate the fault effect and determining which signal (along the path) should be set to what value.

Justification: The process by which the output of any gate is satisfied by values

Figure 2.1: Example Circuit

at its input if many choices exist.

*Propagation:* Fault propagation deals with creating a sensitized path from the fault location to at least one of the PO/PPO. A sensitized path is created if one of the input is sensitized and other non-sensitized inputs are assigned non-controlling values.

*Example:* The fault D s-a-0 needs to be tested. To activate the fault, we require a value 1 on line D. Value 1 on A can be justified in two ways: either E or F are assigned a value of 0 to create a sensitized path between ouput and fault location. Inputs not on the sensitised path, i.e. C and I, are assigned non-controlling values. Value 1 on C can be justified by chossing G or H to justify.

Implication is the process in which all the values can be uniquely assigned by

a given assignment. If B is assigned a value of 0, we know the output of gate A will be 0. Zero at B is said to imply a 0 on A. The above is an example of forward implication. However, a 0 on B does not implies in a backwards direction, as now three choices exist (not uniquely determined or implied) : 0 on D, C, or both.

#### 2.1.1 D-Algorithm

D-algorithm was the first complete algorithm which searches the whole solution space, given that no constraints on run-time exist. D-algorithm uses a five alphabet algebra. The alphabets used are  $\{0, 1, D, \overline{D}, X\}$  where D stands for signal value 1 in good circuit, and 0 in faulty circuit. Similarly,  $\overline{D}$  stands for value 0 in good circuit, and 1 in faulty circuit.

The generation of a test for a stuck-at fault, say line r stuck-at-a, a = 0 or 1, starts by implying value  $\bar{a}$  on line r, where  $\bar{a}$  is the complement of a. This creates a D or  $\bar{D}$  on line r using the D notation introduced in [9]. Next, the value on line r is justified by assigning appropriate values to (some) input(s) of the gate, driving line r, and the D or  $\bar{D}$  on line r is propagated towards the observed outputs through selected intervening gates.

The line justification and propagation of Ds are facilitated by using two data structures called *J*-frontier and *D*-frontier, respectively. The entries in the *J*-frontier are output lines of gates whose outputs have specified values not yet implied by the values of the inputs of the gates. The entries in the *D*-frontier are gates for which some input(s) have D or  $\overline{D}$  values and the outputs are unspecified. Justifying the

required value on a line r in the J-frontier is done by assigning a proper value to one of the inputs of the gate driving r. Propagating D or  $\overline{D}$  to an observed output is done by selecting a gate from the D-frontier and propagating the D or  $\overline{D}$  from its input(s) to its output. The selection of a proper input to be assigned to justify a line value in the J-frontier, and selecting a proper gate from the D-frontier to propagate D or  $\overline{D}$ , is important to obtain tests with a minimum number of specified values, to obtain minimal size test sets and to reduce test generation times. In this work, we will use an ATPG based on D-algorithm for test generation. However, the ATPG is highly enhanced by the use of some other heuristics.

# 2.1.2 PODEM

It was proposed by Goel [10], and aims at using direct search instead of specifying values at internal nodes. PODEM (path oriented decision making) makes all the decisions on the PI/PPI. The major highlights of PODEM are:

- Decisions are made only at primary input, as a result of this no-backward implication is needed in the PODEM.

- Propagation decisions are made by choosing the gate on D-frontier which is closer to the PO/PPO of the gate.

- X-path checking a new method to detect the existence of no solution is introduced. It checks that an unspecified path, x-path, exists between current D-frontier and PO's. If no such path exists, than fault can not be propagated using current D-frontier and a backtrack has to be performed.

- Backtrace is used to justify lines; PI's in the fan-in cone are iteratively assigned values unless the value needed to be justified is satisfied.

- PODEM is a complete algorithm, like D-algorithm, and can generate a test vector if one exists, given no constraint on run time.

- PODEM is approximately 2.5 times faster than D-algorithm, as reported by the author in [10].

The main disadvantage of PODEM is that it has difficulty identifying redundant faults as only assignments to PI are made.

# 2.1.3 FAN

FAN [40] was a successor of PODEM , and borrows some of the ideas of PODEM and D-algorithm. The main highlights of the FAN are:

- Introduces a new concept called unique sensitization. When only one prorogation path exists, we should propagate the D-frontier through it and, at the same time, justify the off-path inputs of gates on the propagation path to non controlling values. It is similar to propagation—first methods described later.

- Does both forward and backward implications like D-algorithm, leading to fast detection of conflicts or redundant faults.

- Unlike PODEM, FAN does not backtrace any J-frontier gates to primary inputs. Instead, it stops at certain circuit lines called headlines. Headlines are the output signals of fanout-free regions. Due to the fanoutfree nature of each cone, all signals outside the cone that do not conflict with the headline assignment

would never require a conflicting value assignment on the primary inputs of the corresponding fanin cone. In other words, any value assignment on the headline can always be justified by its fanin cone. Because each headline has a corresponding fanin cone with several primary inputs, this allows the number of decision points to be reduced.

- Multiple Backtrace: Since we now use unique sensitization, more than one objective may be required to be satisfied simultaneously. Multiple backtrace procedure handles this.

- Usually FAN results in up to 2-5X reduction in test generation time in comparison to PODEM.

# 2.1.4 SOCRATES

The main points about Socrates [41] test generation algorithm are:

- In Socrates [41], both forward and backward implications are used. Also, contrapositive implications are also learned. If we know that (a=0) implies (b=1) then we know (b=0) implies(a=1) is also true.

- 2. While static implications are computed one time for the entire circuit, dynamic implications are updated dynamically during the ATPG process.

- 3. At a given step in the ATPG process, some signals in the circuit would have taken on values, including D or D.

- 4. This set of values may imply other signals which are currently unassigned to necessary value assignments.

5. In general, dynamic implications work locally around assigned signals to see if any implication can be derived.

#### 2.1.5 Recursive Learning

Learning specially dynamic learning is time consuming. Efficient ways were needed especially for hard-to-detect faults. Recursive learning to generate test or declare them redundant for hard-to-detect faults [42]. Recursive learning tries all possible solutions to a problem and finds the intersection set of these solutions. The intersection set must be true for a solution to exist. A complete set of pair-wise implications could be computed. In order to keep the computational costs low, a small recursion depth can be enforced in the recursive learning procedure.

## 2.1.6 SPOP

Single path oriented fault effect propagation (SPOP) [43] is an idea different from traditional ATPGs which consider propagation and justification simultaneously. In SPOP, we first built a sensitized path; after a sensitized path is built, all justified lines are subsequently justified. Creating a sensitized path before justification accelerates the identification of redundant fault.

## 2.2 Test Set Compaction

Compaction techniques can be divided into two sub-categories: dynamic and static compaction. Dynamic compaction technique modifies the ATPG procedure so that every test pattern generated is incrementally specified to detect more unde-

tected faults [29, 30, 31, 32, 35]. Static compaction, however, deals with a complete test set; any generated test set is reordered to modify or drop test patterns that are redundant [32, 33, 34]. Test generation process is not impacted by static compaction. Most of the state-of-the art techniques that result in the smallest test set sizes use a combined approach of static and dynamic compaction. In combined approaches, generally a dynamic compaction procedure is applied first, followed by a static compaction procedure.

Next, we describe some of the previous work in the field of compaction. We discuss test set compaction for scan designs and stuck-at-fault models.

## 2.2.1 Compaction Approach by Goel and Rosales

Authors in [29] were the first to identify the benefits of reducing the test set size by using compaction procedures. Two methods - static and dynamic compaction - were used in this work. In dynamic compaction, a test vector is generated for a fault f. The remaining undetected faults are targeted incrementally by specifying the non-specified positions of the current test vector, where the current test vector is the test vector originally generated for fault f and other faults which were successfully detected by incrementally specifying test vector for f. New faults for given test vectors are targeted until all PIs are specified, or maximum threshold or possibility of success is low. In this work, static and dynamic compaction were not combined and were treated as separate methods.

During static compaction tests for all faults in the test set are generated and

the compatible test vectors are subsequently merged, therefore run time for static compaction was very high.

In the end of the paper, the authors concluded that dynamic compaction procedures are more effective in generating compact test sets in comparison to static compaction procedures. Static compaction procedures take more memory and time as test vectors for all faults in the test sets were targeted.

### 2.2.2 COMPACTEST

Compactest was proposed in [30] and gives one of the best results. Compactest combines the following new concepts to attain a low test set compact test.

- Fault ordering has an impact on test pattern count. Two faults are said to be independent if they do not have a common test vector that detects both of them; example, any stuck-at 1 and stuck-at 0 faults on any input of an AND gate. Independent set fault lists for each FFR are generated and formed into groups. Groups of faults are arranged according to the number of faults in the group. Independent set fault list in an FFR are generated using an efficient algorithm; the largest independent fault list (for FFR's) is targeted first.

- Potential compatible fault list (faults which can be detected by the same vector) is generated and used as an input fault list for dynamic compaction procedure.

- A method named maximal compaction was introduced, which starts with a generated test vector. If any specified PI is non-essential then after inverting the value of that PI if the targeted fault will still be detected by the modified

test vector. Specified position at the PI is not essential and can be changed to X. Commonly, this method is mentioned as relaxation in test literature. Even though it is not guaranteed to be a test, the probability of a relaxed test not being able to detect a previously detected fault is very small.

• Rotating Backtrace: Usually, testability measures are used to guide backtrace decisions. Testability measures are computed once and used for the whole test generation flow. Usually, testability measures guide ATPG toward the easiest possible option. This leads to ATPG being guided toward the same set of nodes, or searching the same search space multiple times. Compaction suffers as ATPG is less likely to be guided toward non-targeted faults. A good way is to rotate between the possible options to facilitate the detection of undetected faults.

# 2.2.3 ROTCO

Reverse Order Test COmpaction (ROTCO) [44] is a static compaction procedure. Its input is a complete test set generated by any other ATPG tool. ROTCO works with faults that were detected only once during the test generation flow. Usually, a lot of inputs remain unspecified even after a complete test set generation. It might be possible to specify these unspecified locations so that a test is generated for some other faults other than those currently detected by the current test vector. If a fault f is detected only once during test set, a test vector  $T_i$  specific to that fault is required in the test set. If by incrementally specifying some other test vector  $T_j$ detects fault f, and no fault exists that is only detected by  $T_i$  in the complete test

set,  $T_i$  is redundant and can be removed from the test set.

The patterns were modified in the reverse order to that of test set generation. This method can be applied even after any dynamic compaction approaches.

# 2.2.4 COMPACT

Compact is a very simple and efficient test generation procedure and has been widely used [31]. The fundamental difference between this and other procedures is, instead of trying to generate a test for a fault by a same vector, it generates vectors individually for faults and merges them Compatible faults usually have similar vectors that can be merged together. The overall approach is described below:

- 1. Generate a test for a set of faults from yet undetected faults. Store it in a buffer.

- 2. Go to the first test vector  $T_i$  in the buffer for fault f; if it is compatible to any other vectors in the buffer, merge the other vectors to  $T_1$ .

- 3. Fault simulate  $T_1$  after merging and drop the faults that are detected by  $T_1$ . Remove the vectors corresponding to these faults if one exists in the buffer.

- 4. If there are undetected faults left, go to step 1.

The main advantage of COMPACT is that the procedure is fast and yet produces reasonably good results.

#### 2.2.5 CODEM

CODEM (Compaction Oriented Decision Making) proposed in [36], was developed for industrial circuits. The main ideas of the approach are as follows:

• Modifies decision making process for test generation to facilitate the detection

of a present set of undetected faults. Both propagation and justification decisions are modified by using a new dynamic testability measure instead of static SCOAP based measures.

- Testability measures are changed so that ATPG is guided in a manner that test vectors for undetected faults are generated by incrementally specifying the unspecified PIs of the test generated for the current targeted fault.

- Testability measures are updated after the generation of every test pattern for a fault, followed by dynamic compaction.

- However, the approach results in only 6% reduction in test length.

- The approach can easily be applied to large industrial circuits, as comparable overheads in terms of memory and run time are low.

- Also, redundant faults were identified in the start of the ATPG process and are used to prevent ATPG from re-targeting redundant faults again, leading to wasted ATPG effort.

# 2.2.6 Double Detection and Two-by One

Double detection and Two by One techniques were proposed in [32]. The improvement was done over COMPACTEST.

# 2.2.6.1 Double Detection

Highlights of the double detection procedure are:

1. *Fault Ordering:* Fault ordering is based on an independent set of faults, with faults in FFR with the largest number of independent faults first. The only

change is that the target list is updated dynamically, based on the current set of undetected faults.

- 2. Changes to Rotatory Backtrace: Rotating backtrace should be used for different vectors, while generating a test for the same vector, it should not be used.

- 3. Double Detection: A test set is generated so that every fault is detected a minimum of two times. Fault simulation is used, and tests that detect essential faults (faults not detected by just one test vector in test set) are simulated first. All the test vectors that do not detect any new faults are dropped. Fault simulation is repeated until every vector contains one essential fault.

# 2.2.6.2 Two-by-One Approach

Two-by-One is a static compaction technique and can be used after generation of any test set. The method works as follows:

- First we extract the essential faults of each test vector.

- In the second step, all independent fault sets are identified. If a fault pair is not independent, two separate vectors are required to generate tests for them.

- If two faults in a pair are not independent, a new test vector is generated that detects all essential faults detected by both vectors. If such a vector is generated, replace both vectors with this new test vector.

- If any such pair of faults still exist, repeat the procedure for them.

Experimental results showed that the combination of double detection, two by one, improved fault ordering, and improved backtrace procedure gives shorter test

length than if each of these procedures were used individually.

# 2.2.7 Set Cover Method

This paper maps the test compaction problem to a set cover problem [45]. In this case, the problem was mapped to airline scheduling problems. The problem can be thought of as the following:

- Suppose test vectors are sets and faults are elements in a set.

- Set cover problem is defined as a minimum number of sets (test vectors) that are required to cover all elements (faults).

- The problem is known to be an NP Complete problem, so no good solution exists. The only hope is to use an approximate solution.

- The problem was mapped to airline scheduling problems, and an LP relaxation based solution was proposed.

- Since the number of faults is huge, only a given number of faults are considered once and a solution is generated for them.

The solution resulted in a good test length, and can even reduces the test length of some previously known procedures.

# 2.2.8 Mintest

The Mintest works on two techniques [35]: essential fault removal (EFR) and redundant vector elemination (RVE). In EFR, a test vector is taken and all essential faults are assigned to other vectors, by incrementally specifying them. Even if all the essential faults can not be assigned to other vectors the status of vectors are preserved

and the possibility of removal is increased, as some vectors that are redundant may be left with fewer faults after each iteration. Fewer essential faults may lead to increased probability of the essential faults being assigned to other vectors.

## 2.2.9 Forward Looking Fault Simulation

Reverse-order fault simulation (ROFS) was found to be efficient in quickly reducing the size of a test set. However, with only ROFS, it is possible for some redundant vectors that don't contain any essential fault to be retained. Prior to using the technique [46], the original test set is simulated and each fault is associated with an index which links to the vector that first detects the fault. Next, the test set is re-simulated in reverse order. A fault is dropped from the fault list as soon as it is detected by a vector. A vector i is dropped in this process if either it detects no new fault, or no fault it detects has index i.

If no fault detected by i has index i, that means there is at least another vector that detects the fault that will be simulated in the future. Hence, there is no need to keep vector i since all faults it detects are going to be detected by later vectors. Experimental results showed that using forward-looking fault simulation yields a more compact test set than using reverse-order fault simulation.

## 2.2.10 Pattern Generation for Embedded BIST

In this work [47] the authors used a hybrid BIST scheme where random patterns are applied first, and then patterns are generated for a BIST scheme having constraints on encoding. Only a given number of specified positions can be encoded

in every cycle. The ATPG has some interesting highlights :

- ATPG was guided based on undetected faults.

- If no undetected fault detection is facilitated by ATPG, a decision leading to the minimum number of specification is used.

- If D-frontier has a controlling value for gate on propagation path, any faults on the other inputs of the gate are not observable and no faults in the fan-in of these input can be detected, leading to a minimum specification decision.

- Both static and dynamic compaction schemes were used to generate compact tests for embedded BIST.

#### 2.2.11 Tests With Large Number of Unspecified Bits

In this work a dynamic and static compaction scheme was proposed for circuits with a large number of unspecified bits.

- *Static Compaction:* A given test vector is considered, and specified bits are relaxed so that all essential faults detected by the compaction schemes are detected even after relaxation and fewer specified bits.

- Dynamic Compaction: A fault is considered compatible if a single test detects a fault, possibly with less number of specified bits. A compatibility graph is constructed so that the vertices's in the graph consists of fault, and the edge weight represents the number of specified bits if two faults are compatible. At first a few faults are targeted and compatibility relations are explored by merging compatible faults together if a test vector detecting both of them with a low

number of specifications exists. In later operations, more faults are considered.

## 2.2.12 Delayed Justification

Delayed justification approach was proposed in [39]; it has long been known that headlines [40] can be justified later during the test generation process. The same concept is applied to compression with some modifications:

- Headlines are identified not only statically but dynamically, depending on the circuit node values; this leads to an increase in the number of headlines.